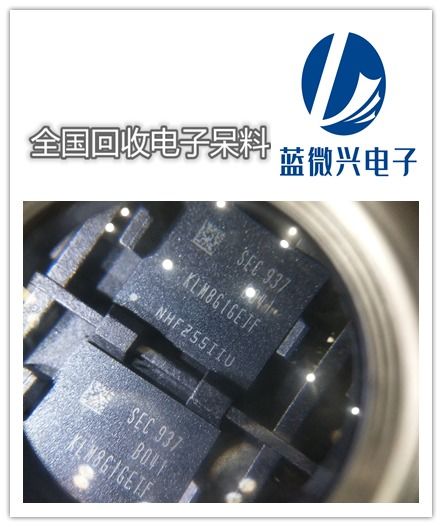

基于LTC6951的5輸出整數N PLL集成VCO的參考設計 DC2248A-A演示板詳解

在高速通信、測試測量和雷達系統中,高性能、低噪聲的時鐘生成與分配至關重要。LTC6951作為一款先進的整數N分頻鎖相環(PLL)芯片,集成了壓控振蕩器(VCO),能夠提供多個超低抖動、高精度的同步時鐘輸出。與之配套的DC2248A-A演示板,則為工程師提供了一個功能完整、易于評估和快速原型開發的參考設計平臺。本文將深入探討該演示板的設計理念、核心芯片特性及其在集成電路設計服務中的應用價值。

一、核心芯片LTC6951:高性能時鐘解決方案的核心

LTC6951是一款由亞德諾半導體(Analog Devices)推出的高性能整數N PLL。其核心優勢在于集成了寬帶、低噪聲的VCO,頻率范圍覆蓋62.5 MHz至2 GHz,無需外部VCO元件,極大地簡化了系統設計并節省了電路板空間。芯片支持整數N分頻模式,能夠根據參考時鐘精確合成所需的輸出頻率。

關鍵特性包括:

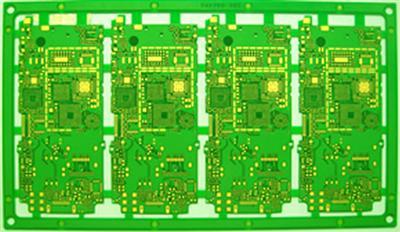

1. 多路超低抖動輸出:提供多達5路獨立的時鐘輸出通道(其中4路為LVDS/CMOS可選,1路為固定LVDS)。每路輸出均可獨立分頻和調整相位,相位噪聲和抖動性能卓越,尤其適合驅動高速ADC、DAC或作為FPGA的同步時鐘源。

2. 集成VCO與環路濾波器:內部集成VCO減少了對外部元件的依賴,降低了設計復雜性和噪聲引入點。其靈活的環路濾波器架構允許用戶針對不同的相位噪聲、鎖定時間和參考雜散指標進行優化。

3. 靈活的配置與監控:通過SPI接口可對分頻比、輸出格式、功率等所有參數進行數字編程。芯片還集成了鎖定檢測和同步功能,確保多路輸出之間精確的相位關系,便于系統同步。

二、DC2248A-A演示板:從評估到集成的橋梁

DC2248A-A演示板是一個經過充分驗證的硬件平臺,旨在全面展示LTC6951在真實工作環境下的性能。它不僅僅是一塊評估板,更是一個完整的參考設計,為工程師提供了可直接借鑒或修改的設計藍圖。

演示板的主要構成與功能:

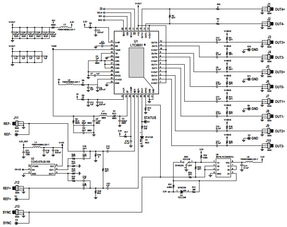

1. 完整的信號鏈:板上集成了LTC6951芯片、必要的電源管理電路、高精度參考時鐘輸入接口(如100MHz OCXO或外部輸入)、以及5路時鐘輸出的連接器(通常為SMA接口),構成了一個立即可工作的時鐘生成系統。

2. 直觀的配置與測試:板載的USB接口可通過配套軟件(如ADI的PLLWizard)連接電腦,實現圖形化參數配置和實時性能監控。工程師可以輕松測試不同頻點、分頻比下的相位噪聲、抖動和鎖定時間,加速設計決策。

3. 優化的布局與布線:演示板的PCB布局嚴格遵循高速、低噪聲設計原則,例如為PLL內核和輸出緩沖器提供獨立的低噪聲電源層、優化去耦電容布局、控制傳輸線阻抗等。這些細節是保證芯片達到標稱性能的關鍵,為用戶的自主設計提供了寶貴的參考。

三、在集成電路芯片設計及服務中的應用

對于提供集成電路設計及服務的企業或團隊而言,LTC6951和DC2248A-A演示板的價值體現在多個層面:

- 加速客戶系統開發:在為客戶提供定制化系統解決方案時,尤其是涉及高速數據采集、相控陣雷達或多通道同步測試設備時,可以直接推薦或采用此成熟方案。利用演示板進行快速原型驗證,能顯著縮短客戶的研發周期,降低技術風險。

- 作為內部設計的性能標桿:在進行自主時鐘芯片或包含時鐘模塊的SoC設計時,LTC6951的架構和性能參數可以作為重要的設計參考和驗證基準。DC2248A-A的布局布線經驗,對于提升自身芯片的板級應用性能具有直接的指導意義。

- 提供增值技術服務:設計服務團隊可以基于該平臺,為客戶提供更深入的時鐘樹設計、抖動分析、系統同步方案優化等專業服務。演示板成為了一個強大的演示和調試工具,增強了服務的專業性和說服力。

- 教學與培訓:該平臺也是培訓新工程師理解高性能PLL系統設計、噪聲分析和PCB布局技術的絕佳實物教材。

結論

LTC6951集成VCO的整數N PLL與DC2248A-A演示板的組合,代表了一個經過生產驗證的高端時鐘解決方案。它通過高度集成的芯片設計和精心優化的參考硬件,將復雜的時鐘系統設計轉化為可快速部署的工程實踐。對于任何致力于高性能電子系統開發的工程師或集成電路設計服務提供商而言,深入理解和利用這一參考設計,無疑是提升產品競爭力、確保系統時序性能并加速項目上市進程的有效途徑。從評估評估到最終產品集成,DC2248A-A演示板架起了一座從理論到可靠實現的堅實橋梁。

如若轉載,請注明出處:http://www.toesocks.cn/product/84.html

更新時間:2026-04-14 16:09:42